# IDEC Chip Design Contest

# KAIST

# A 28/37-GHz Frequency-Reconfigurable Front-End IC for Millimeter-Wave 5G Handsets

Gyuha Lee\*, Jaehun Lee\*\*, Hyoungkyu Jin\*\*, and Songcheol Hong\*

\*Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Daejeon, Republic of Korea

\*\*System LSI Business, Samsung Electronics, Hwaseong, Republic of Korea

#### Introduction

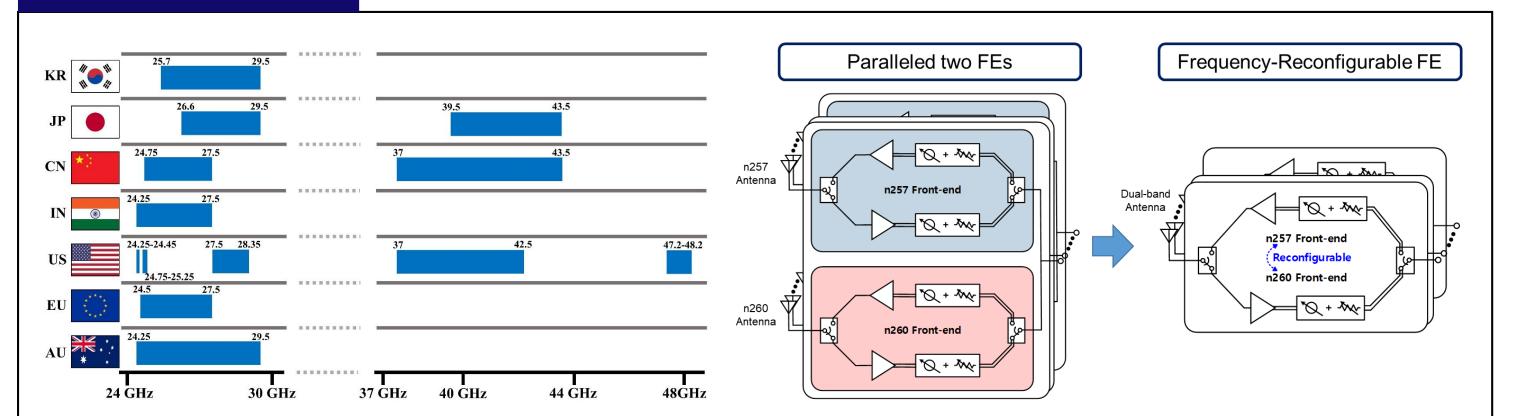

### [ Global 5G Spectrum ]

- Different countries use different frequency bands.

- → Dual-band front-end IC is needed for global usage & roaming service.

#### [ Dual-band front-end structure ]

■ Frequency-reconfigurable (FR) front-end can halve the form factor compared to conventional structure (paralleled two single-band front-ends).

#### Schematic Design

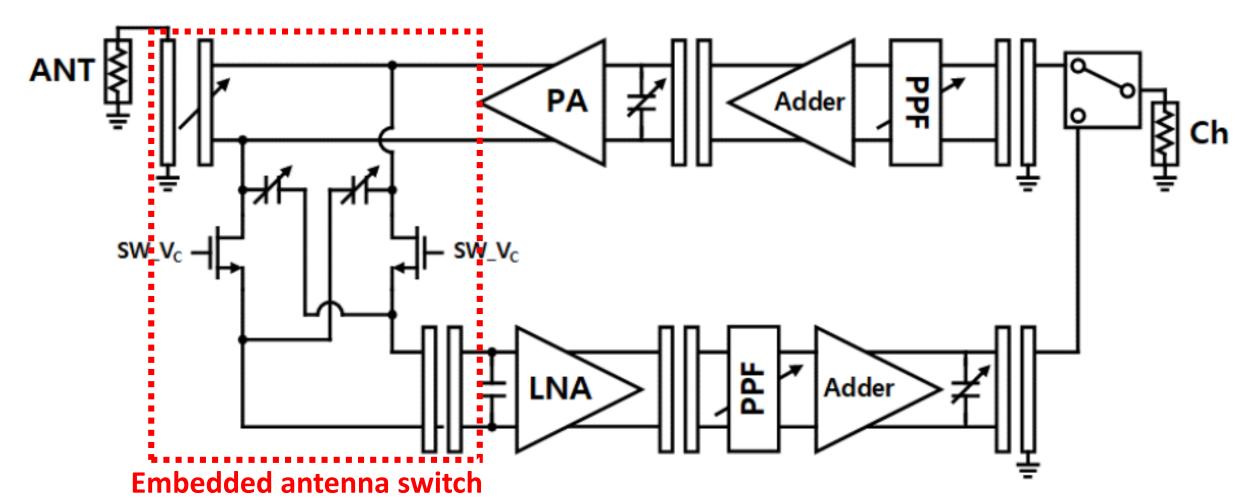

Proposed FR dual-band front-end IC

[ Block diagram of FR front-end IC]

- Proposed IC consists of dual-band LNA, channel switch, and FR PA variable-gain phase shifter, embedded antenna switch [1].

- Embedded antenna switch consists of FR TLT for TX mode impedance matching, SPST switch for TRx mode change, and TLT for RX mode impedance matching.

[1] RFIC 2023 – A 28/37 GHz Frequency Reconfigurable Dual-Band Beamforming Front-End IC for 5G NR

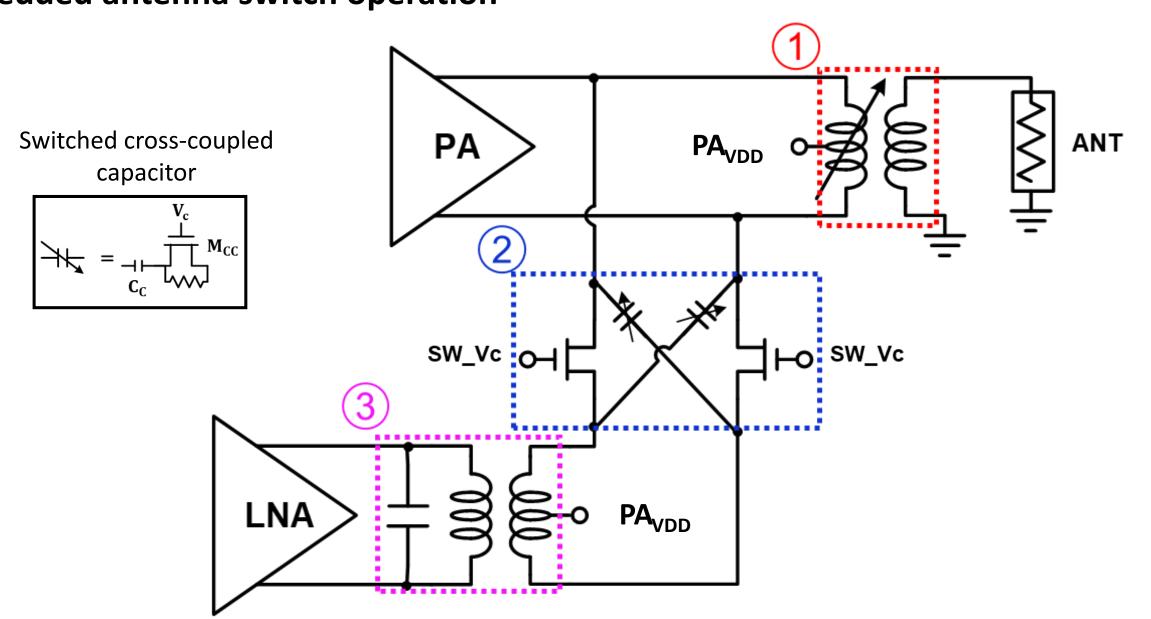

# Embedded antenna switch operation

[ Block diagram of the embedded antenna switch ]

# ① TX FR TLT

- PA impedance matching  $(Z_{opt,PA} \leftrightarrow 50\Omega)$ .

- ② SPST switch with switched cross-coupled capacitor

- TX mode: Cancel parasitic off-capacitance of the switch transistor to reduce the leakage.

RX mode: Act as a matching network (shunt capacitor).

- 3 RX TLT with shunt capacitor

- RX impedance matching  $(Z_{opt,PA} \leftrightarrow Z_{opt,LNA})$ .

- Bias condition

- TX mode:  $PA_{VDD}$ =2.2V,  $SW_Vc=1.1V$ .

- RX mode: PA<sub>VDD</sub>=1.1V, SW\_Vc=2.2 V.

# Acknowledgement

The chip fabrication and EDA tools were supported by Samsung Co. Ltd., and IC Design Education Center(IDEC), respectively.

### Implementation and Measurement Results

Chip implementation & Measurement Setup

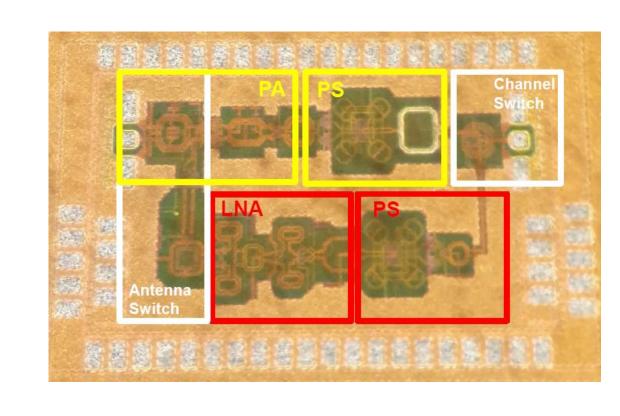

#### [Chip photograph]

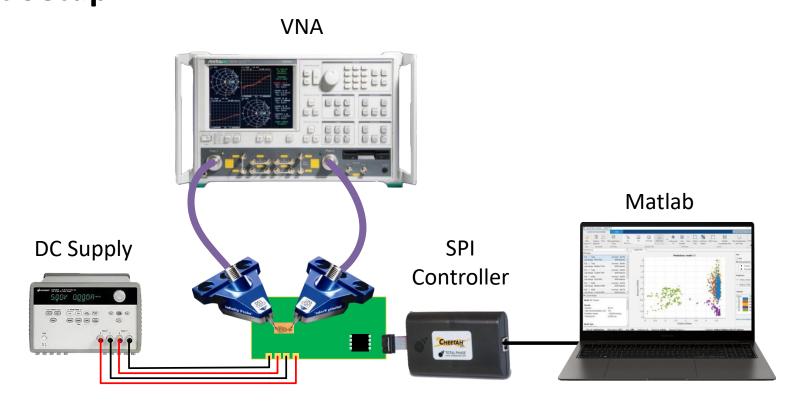

[ S-Parameter measurement setup ]

- Process: Samsung 28nm bulk CMOS.

- Size:  $1287 \times 756 \ \mu\text{m}^2$  (core),  $1886 \times 1143 \ \mu\text{m}^2$  (total).

- Electro-Magnetic field simulated by Keysight ADS Momentum.

- Phase/Gain state is controlled by Cheetah SPI Controller and Matlab.

#### Measurement results

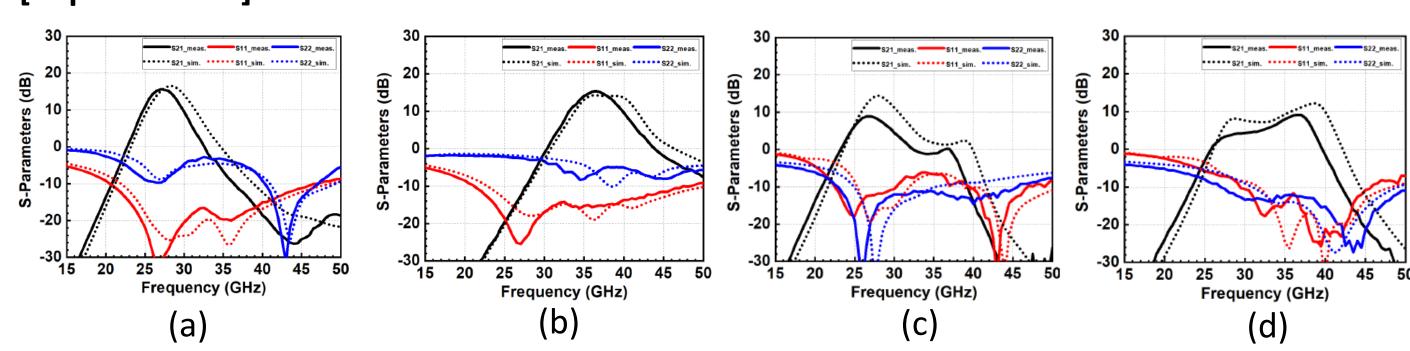

#### [ S-parameter ]

TX mode gain of 15.1/15.1 dB and RX mode gain of 8.9/9.2 dB at 28/37 GHz.

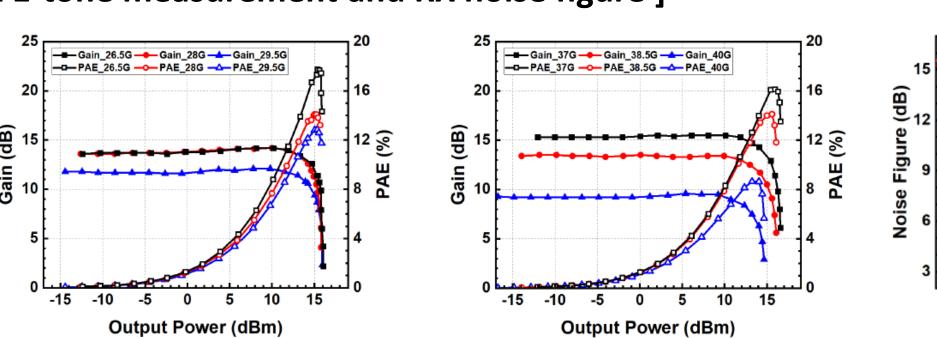

# [ TX 1-tone measurement and RX noise figure ]

- TX OP1dB of 14.3/14.1 dBm and TX Psat of 15.8/16.6 dBm at 28/37 GHz.

- Peak PAE of 14.1/16.1% at 28/37 GHz.

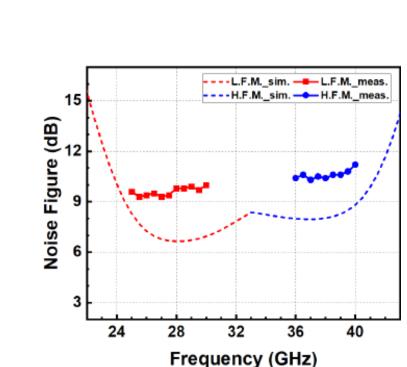

- Noise figure of 9.3/10.3 dB at 28/37 GHz.

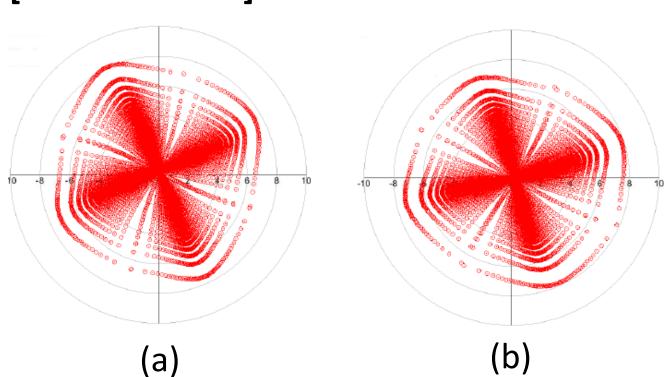

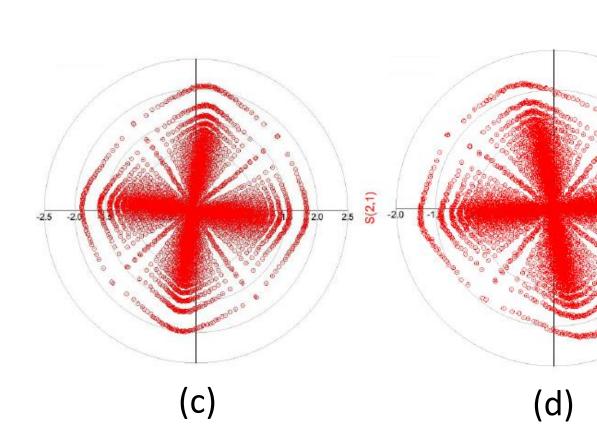

## [Constellation]

- The overall gain/phase states (a) TX 28 GHz, (b) TX 37 GHz, (c) RX 28 GHz, and (d) RX 37 GHz.

- 6-bit gain control, 7-bit phase control, and 16 dB gain dynamic range.

# [ Comparison table ]

|            |               |             | RX        |         | TX        |            |            |         |                 |

|------------|---------------|-------------|-----------|---------|-----------|------------|------------|---------|-----------------|

|            | Technology    | Freq. (GHz) | Gain (dB) | NF (dB) | Gain (dB) | Psat (dBm) | P1dB (dBm) | PAE (%) | Core area (mm²) |

| RFIC 2024  | 65 nm<br>CMOS | 27          | 16        | 6.7*    | 24*       | 17.6       | 13*        | 19      | 0.78            |

|            |               | 37          | 15        | 8.1     | 27        | 16.4       | 13.6       | 12.2    |                 |

| ISSCC 2020 | 65 nm<br>CMOS | 28          | 44        | 8.5*    | 43.5      | 15.5       | 14         | 21      | 1.05            |

|            |               | 37          | 37        | 9.5*    | 40        | 15.6       | 14.2       | 21.5    |                 |

| TMTT 2020  | 45 nm<br>CMOS | 28          | 19.3      | < 4     | 17.6      | 19.2*      | 16*        | 18      | _               |

|            |               | 36          |           |         | 13.6      | 18.8*      | 15*        | 14.1    |                 |

| ISSCC 2019 | 65 nm<br>CMOS | 28          | 16.1      | 7.4*    | 28.5      | 15.8       | 14.1       | 20      | _               |

|            |               | 37          | 10.9      | 7*      | 26.2      | 16.8       | 15.2       | 21.6    |                 |

|            |               | 39          | 8.3       | 7.9*    | 20.3      | 16.7       | 13.5       | 22.2    |                 |

| This work  | 28 nm<br>CMOS | 28          | 8.9       | 9.3     | 15.1      | 15.8       | 14.3       | 14.1    | 0.97            |

|            |               | 37          | 9.2       | 10.3    | 15.1      | 16.6       | 14.1       | 16.1    |                 |

### Conclusions

\*Graphically estimated

A 28/37 GHz transmitter-optimized FR front-end IC utilizing an embedded antenna switch is implemented and verified. The antenna switch is integrated in TX matching network with TLTs and an SPST switch. The proposed dual-band front-end IC shows high TX performance, as the output power for PA directly connected to antenna.